Inhalt:

- R³ckblick

- Bulldozer Architektur vom Vorgõnger

- AMD RYZEN Prozessor

- AMD ZEN-Architektur

- Bestandteile des AMD RYZEN äSystem on Chipō

- Speichercontroller

- PCI Express Anbindung f³r Grafikkarten:

- AMD I/O-Hub-Anbindung

- SATA, NVMe, USB-Schnittstellen, Audio-Codec, BIOS und Sonstiges

- AMD RYZEN Features

- AMD Simultaneous Multithreading

- SenseMI, Precision Boost und PurePower

- AMD AM4 Plattform

- I/O-Hubs

- Benchmarking

- Testsysteme

- Spiele- und grafiklastige Benchmarks

- Gesamtsystem / isolierte CPU-Tests

- Fazit

- Ausblick und Empfehlung

R³ckblick

Vor 6 Jahren und knappe 7 Monaten hat AMD die erste Generation der damals vielversprechenden Bulldozer-Architektur herausgebracht. Leider floppte die Architektur und lie▀ den FX-Hype am rabenschwarzen Mittwoch untergehen.Bulldozer Architektur vom Vorgõnger

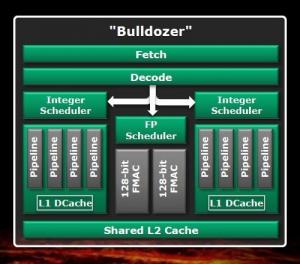

Die Bulldozer-Architektur setzt als wichtigstes Merkmal auf das CMT (Core-Multithreading) und somit besteht ein Prozessor aus mindestens einem Modul. Pro Modul werden zwei x86-Rechenkerne eingesetzt und diese m³ssen sich eine FPU (Floating-Point-Unit) teilen. Die Befehle werden bei der Bulldozer-Architektur durch einen Fetch-Bereich eingelesen. Im Decode-Bereich wird der Prozess entsprechend sortiert. Integer-Rechenoperationen werden zu den Integer-Schedulern geschickt, dort werden diese in Pipelines aufgearbeitet.

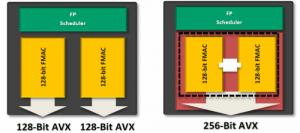

Floating-Point-Operationen werden ³ber den FP-Scheduler geleitet. In 128 Bit breiten Registern werden diese Operationen ausgewertet. Durch das Addieren der beiden Pipelines sind 256 Bit breite Register vorhanden. So kann AMD mit der Bulldozer FPU gleichzeitig zwei 128-Bit breite AVX Befehle ausf³hren, oder beide Register addieren lassen und so nacheinander 256 Bit breite AVX-Befehle ausf³hren. AMD nennt diese Technologie FMA (Fused Multiply Add). Bei der FMA-Technologie wird im Gegensatz zur Intels 256 Bit AVX am Ende des Rechenprozesses gerundet und besitzt damit eine h÷here Genauigkeit. Der Vorteil wird bei AES (Advanced Encryption Standard) und anderen Verschl³sselungssystemen genutzt und bietet im Vergleich zu der damaligen Phenom-Generation eine bis zu 10-fache Leistung.

AMD gab im Vorfeld an, dass die Leistung jedes Moduls etwa 180 % an Leistung eines einzelnen Cores konventioneller Bauweise entspricht.

Die MultiCore-Leistung der Architektur war f³r damalige Zwecke gro▀artig. Wenn dem Prozessor jedoch nur einen einzelnen Befehl verarbeiten musste, brach im Vergleich zu anderen Architekturen aus der Zeit die Leistung enorm ein.

Teilweise konnte AMD dieses Problem mit Architektur-▄berarbeitung bei den Piledriver-Prozessoren ausb³geln und verpasste diesem eine verbesserte Sprungvorhersage.

Nach dem Update auf Piledriver folgte f³r die (Accelerated Prozessor Units) APUs noch die Steamroller- und die Excavator-Architektur. Diese konnte die Leistungsfõhigkeit und die IPC (Instructions per Circle) nochmals wesentlich erh÷hen. F³r Enthusiast-Anwender hat AMD diese neuen Architekturen jedoch grob vernachlõssigt.